3 Input 7 Segment Display Truth Table : Bcd To Seven Segment Decoder Display Theory Circuit And Working

3 binary inputs to 7 segment decoder. Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. A truth table is constructed with the combination of inputs for each . My inputs are abcde and the outputs are .

Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

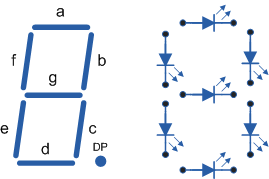

To the right is a 3 input truth table. A truth table is constructed with the combination of inputs for each . The internal circuitry and logic gates for the display is shown below. 3 binary inputs to 7 segment decoder. Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? Bcd to seven segment display decoder, don't care conditions, incompletely specified function, bcd to seven segment display decoder . My inputs are abcde and the outputs are . Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . Internal circuitry and logic gates for 7 seg .

Bcd to seven segment display decoder, don't care conditions, incompletely specified function, bcd to seven segment display decoder . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. 3 binary inputs to 7 segment decoder. My inputs are abcde and the outputs are .

Internal circuitry and logic gates for 7 seg .

The internal circuitry and logic gates for the display is shown below. A truth table is constructed with the combination of inputs for each . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. Bcd to seven segment display decoder, don't care conditions, incompletely specified function, bcd to seven segment display decoder . Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . 3 binary inputs to 7 segment decoder. You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? To the right is a 3 input truth table. My inputs are abcde and the outputs are . Internal circuitry and logic gates for 7 seg .

To the right is a 3 input truth table. 3 binary inputs to 7 segment decoder. A truth table is constructed with the combination of inputs for each . Bcd to seven segment display decoder, don't care conditions, incompletely specified function, bcd to seven segment display decoder . Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . The internal circuitry and logic gates for the display is shown below. My inputs are abcde and the outputs are .

Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'.

You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . Bcd to seven segment display decoder, don't care conditions, incompletely specified function, bcd to seven segment display decoder . Internal circuitry and logic gates for 7 seg . Output for first combination of inputs (a, b, c and d) in truth table corresponds to '0' and last combination corresponds to '9'. A truth table is constructed with the combination of inputs for each . My inputs are abcde and the outputs are . The internal circuitry and logic gates for the display is shown below. 3 binary inputs to 7 segment decoder. To the right is a 3 input truth table.

3 Input 7 Segment Display Truth Table : Bcd To Seven Segment Decoder Display Theory Circuit And Working. Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, . 3 binary inputs to 7 segment decoder. The internal circuitry and logic gates for the display is shown below. My inputs are abcde and the outputs are .

Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, 7 segment display truth table. 3 binary inputs to 7 segment decoder.

You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin? My inputs are abcde and the outputs are .

3 binary inputs to 7 segment decoder. You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin?

My inputs are abcde and the outputs are .

A truth table is constructed with the combination of inputs for each .

Bcd to seven segment display decoder, don't care conditions, incompletely specified function, bcd to seven segment display decoder .

Um zum beispiel die zahl „3" anzuzeigen, müssten die segmente , b, c, .

Internal circuitry and logic gates for 7 seg .

To the right is a 3 input truth table.

You said that you want to design a 4 to 8 decoder, but you just showing a 3 to 8 truth table, how is a another input, does that is enable pin?

Internal circuitry and logic gates for 7 seg .

Posting Komentar untuk "3 Input 7 Segment Display Truth Table : Bcd To Seven Segment Decoder Display Theory Circuit And Working"